## ВАЛУЕВА МАРИЯ ВАСИЛЬЕВНА

# РАЗРАБОТКА МЕТОДОВ И АЛГОРИТМОВ ПОСТРОЕНИЯ ЦИФРОВЫХ УСТРОЙСТВ ИНТЕЛЛЕКТУАЛЬНОГО АНАЛИЗА ВИЗУАЛЬНЫХ ДАННЫХ

Специальность: 2.3.5 – Математическое и программное обеспечение вычислительных систем, комплексов и компьютерных сетей

Автореферат диссертации на соискание ученой степени кандидата технических наук Работа выполнена на кафедре вычислительной математики и кибернетики факультета математики и компьютерных наук имени профессора Н.И. Червякова федерального государственного автономного образовательного учреждения высшего образования «Северо-Кавказский федеральный университет» (ФГАОУ ВО СКФУ).

#### Научный руководитель:

#### Бабенко Михаил Григорьевич

доктор физико-математических наук, доцент, заведующий кафедрой вычислительной математики и кибернетики факультета математики и компьютерных наук имени профессора Н.И. Червякова

ФГАОУ ВО СКФУ, г. Ставрополь

#### Официальные оппоненты:

#### Феоктистов Александр Геннадьевич,

доктор технических наук, доцент, главный научный сотрудник лаборатории параллельных и распределенных вычислительных систем, Федеральное государственное бюджетное учреждение науки Институт динамики систем и теории управления имени В.М. Матросова Сибирского отделения Российской академии наук

#### Исупов Константин Сергеевич,

кандидат технических наук, доцент кафедры электронных вычислительных машин, Федеральное государственное бюджетное образовательное учреждение высшего образования «Вятский государственный университет»

## Ведущая организация:

Федеральное государственное автономное образовательное учреждение высшего образования «Южный федеральный университет»

Защита состоится 19 октября 2023 г. в 15 часов на заседании диссертационного совета 24.1.120.01 при Федеральном государственном бюджетном учреждении науки Институте системного программирования им. В.П. Иванникова Российской Академии Наук по адресу: 109004, г. Москва, ул. А. Солженицына, д. 25.

С диссертацией можно ознакомиться в библиотеке и на сайте Федерального государственного бюджетного учреждения науки «Институт системного программирования им. В.П. Иванникова Российской Академии Наук».

| Автореферат разосл | ıан « | <b>&gt;&gt;</b> | 2023 г. |

|--------------------|-------|-----------------|---------|

|                    |       |                 | _       |

Ученый секретарь диссертационного совета 24.1.120.01, кандидат физико-математических наук

Зеленов С.В.

#### Общая характеристика работы

Актуальность работы. Современные алгоритмы интеллектуального анализа информации требуют больших вычислительных затрат и ресурсов для их реализации. Для решения данной проблемы на практике зачастую используются удаленные вычислительные ресурсы, такие как большие центры обработки данных, облачная инфраструктура и другие. Но такие способы подходят не для всех практических задач, использующих решения на основе искусственного интеллекта на сегодняшний день. Одним из основных методов решения задач в области искусственного интеллекта являются глубокие нейронные сети. Нейросетевые интеллектуальные системы используют значительное количество памяти и времени на этапе обучения искусственной нейронной сети, кроме того, на этапе эксплуатации важно обеспечивать работу системы в режиме реального времени. Это побуждает исследователей вести разработку специализированных аппаратных ускорителей нейросетевых вычислений.

Постоянно растущая практическая потребность в увеличении скорости и энергоэффективности работы устройств делает актуальной проблему качественного развития аппаратных ускорителей нейросетевых вычислений для обеспечения быстрой работы и экономически выгодной эксплуатации таких систем. Решение проблемы улучшения технических характеристик аппаратных реализаций глубоких нейронных сетей позволит существенно расширить применение интеллектуальных технических средств в практической деятельности человека. Успешное решение обозначенной проблемы окажет большое влияние на развитие таких практических приложений как распознавание изображений, анализ речи и создание робототехнических систем.

В настоящее время существуют аппаратные реализации простых нейронных сетей, в том числе осуществляющих и процесс обучения нейронной сети. Но архитектура глубокой нейронной сети имеет весьма сложную структуру, вследствие чего разработка микроэлектронных устройств на ее основе с аппаратной реализацией процесса обучения является малоисследованной областью. Одним из эффективных путей повышения качества проблемно-ориентированных процессоров является оптимизация вычислений на арифметическом уровне.

Среди различных альтернативных числовых систем особый интерес представляет система остаточных классов (СОК), способная обеспечить параллельную реализацию арифметических операций, в особенности сложения и умножения. СОК представляет собой прямую сумму конечных колец и оперирует с небольшими остатками вместо обработки чисел большой разрядности в позиционных системах счисления (ПСС), что открывает возможности для параллельной обработки данных на арифметико-логическом уровне.

Значительный научный вклад в теорию модулярных вычислений и их приложений внесли отечественные и зарубежные исследователи: И.Я. Акушский, Д.И. Юдицкий, В.М. Амербаев, А.А. Коляда, Н.И. Червяков, О.А. Финько, N. Szabo, D. Svoboda, M. Valach, H.L. Garner, B. Parhami, A. Omondi, A. Premkumar, J. Ramires, L. Sousa и другие.

<u>Целью диссертационного исследования</u> является увеличение производительности системы обработки и анализа изображений в условиях ограниченности ресурсов, требующихся для построения и эксплуатации системы.

Объект исследования – системы обработки и анализа изображений.

<u>Предмет исследования</u> — свойства и принципы функционирования систем анализа визуальных данных.

<u>Научная задача</u> — разработка методов проектирования аппаратных ускорителей системы интеллектуального анализа изображений для повышения их производительности.

Для решения поставленной общей научной задачи произведена ее декомпозиция на ряд частных задач:

- 1. Разработка математической модели сверточных нейронных сетей (СНС) с реализацией вычислений в СОК для создания высокопроизводительных систем интеллектуального анализа изображений.

- 2. Разработка методов проектирования аппаратных ускорителей компонентов СНС, выполняющих вычисления в СОК, и их реализация на языке описания аппаратуры.

- 3. Разработка алгоритма проектирования аппаратной реализации СНС с вычислениями в СОК.

- 4. Разработка программного комплекса на языке описания аппаратуры VHDL для аппаратной реализации CHC для распознавания образов с использованием модулярных вычислений на FPGA (Field-Programmable Gate Array).

Соответствие паспорту научной специальности. Область исследования соответствует паспорту специальности 2.3.5 — Математическое и программное обеспечение вычислительных систем, комплексов и компьютерных сетей по следующим пунктам:

- 7. Модели, методы, архитектуры, алгоритмы, форматы, протоколы и программные средства человеко-машинных интерфейсов, компьютерной графики, визуализации, обработки изображений и видеоданных, систем виртуальной реальности, многомодального взаимодействия в социокиберфизических системах.

- 8. Модели и методы создания программ и программных систем для параллельной и распределенной обработки данных, языки и инструментальные средства параллельного программирования.

<u>Методы исследования.</u> Для решения поставленных задач были использованы методы алгебры, линейной алгебры, теории чисел, теории модулярных вычислений в

системе остаточных классов, теории алгоритмов, методы математического и имитационного моделирования.

#### Научная новизна:

- 1. Разработана математическая модель СНС с реализацией вычислений в СОК, которая отличается от известных тем, что использует набор модулей специального вида и не требует выполнения обратного преобразования в позиционную систему счисления (ПСС) для выполнения вычислительно сложных операций в СОК в скрытых слоях СНС.

- 2. Разработан метод проектирования сверточных слоев СНС и его программная реализация на языке описания аппаратуры VHDL, отличающийся от известных тем, что основывается на методе Винограда и использует арифметику СОК с модулями специального вида.

- 3. Разработаны методы, проектирования функции активации ReLU (Rectified Linear Unit) и слоя выборки максимального элемента из окрестности, требующие выполнения вычислительно сложных операций в СОК, и их программная реализация на языке описания аппаратуры VHDL.

- 4. Разработан алгоритм проектирования аппаратной реализации СНС, отличающийся от аналогов тем, что учитывает выбор модулей СОК, способ представления весовых коэффициентов в памяти устройства и оригинальные методы проектирования компонентов СНС.

- 5. Разработан комплекс программ на языке описания аппаратуры VHDL для аппаратной реализации CHC для распознавания образов с использованием модулярных вычислений на FPGA, которая разработана на основе оригинального алгоритма проектирования CHC в COK.

<u>Достоверность</u> полученных в диссертации результатов подтверждается результатами математического и имитационного моделирования и анализом эффективности разработанных методов и алгоритмов.

<u>Моделирование и вычислительный эксперимент</u> проведены с использованием языка высокого уровня Python в среде PyCharm для обучения СНС, а также с использованием языка описания аппаратуры VHDL и среды автоматизированного проектирования Xilinx Vivado для аппаратной реализации СНС.

<u>Практическая ценность.</u> Разработанные в рамках диссертационного исследования алгоритмы для проектирования аппаратных ускорителей СНС и комплекс программ, использующих модулярные вычисления, внедрены в организации ООО «Инфоком-С» в системе интеллектуального реагирования на инциденты и события «Darvis».

## Положения, выносимые на защиту:

1. Метод преобразования чисел из ПСС в СОК с модулями специального вида и его программная реализация на языке описания аппаратуры.

- 2. Метод проектирования устройства, реализующего операцию свертки на основе метода Винограда и СОК с модулями специального вида, и его программная реализация на языке описания аппаратуры.

- 3. Метод проектирования устройства, реализующего функцию активации ReLU на основе Китайской теоремы об остатках с дробными величинами (КТОд), и его программная реализация на языке описания аппаратуры.

- 4. Метод проектирования устройства, реализующего операцию выбора максимального элемента из окрестности на основе КТОд, и его программная реализация на языке описания аппаратуры.

- 5. Алгоритм проектирования аппаратной реализации СНС, учитывающий выбор модулей СОК, способ представления весовых коэффициентов в памяти устройства и методы проектирования компонентов СНС в СОК.

- 6. Комплекс программ на языке описания аппаратуры для аппаратной реализации СНС с использованием модулярных вычислений на FPGA, который разработан на основе оригинального алгоритма проектирования СНС в СОК.

Внедрение. Результаты диссертационного исследования использованы при выполнении научно-исследовательских проектов Совета по грантам Президента РФ СП-126.2019.5 «Разработка микроэлектронных устройств интеллектуального анализа визуальных данных», МК-3918.2021.1.6 «Высокопроизводительные устройства цифровой обработки медицинских изображений на основе параллельной математики», РФФИ 18-37-20059-мол\_а\_вед «Разработка перспективной архитектуры на базе ядра векторного процессора для задач обработки и визуализации сигналов», 19-07-00130-А «Экономические средства интеллектуального анализа визуальной информации на основе сверточных нейронных сетей», Минобрнауки № 13.2251.21.0064 «Фундаментальные алгоритмы, технологии глубокого обучения и безопасности для облачного хранения и обработки данных» и Министерства науки и высшего образования Российской Федерации № 075-15-2020-788 «Исследование и разработка передовых методов защиты информации, сохранения конфиденциальности и предотвращения утечки данных при обработке данных в распределенных средах».

Апробация работы. Результаты диссертационного исследования прошли апробацию на научных мероприятиях всероссийского и международного уровней: International Multi-Conference on Engineering, Computer and Information Sciences (SIBIRCON) 2017, 10th Mediterranean Conference on Embedded Computing (MECO) 2021, 9th Mediterranean Conference on Embedded Computing (MECO) 2020, IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (ElConRus) 2020, International Conference on Engineering and Telecommunication (EnT) 2019, 42nd International Conference on Telecommunications and Signal Processing (TSP) 2019, 23rd

Conference of Open Innovations Association (FRUCT) 2018, Third International Conference on Digital Information Processing, Data Mining, and Wireless Communications (DIPDMWC) 2016, форум «Наука будущего – наука молодых» 2017.

<u>Публикации по теме диссертации.</u> Основные результаты исследования отражены в 33 работах, среди которых 12 статей в научных изданиях, входящих в перечень ВАК и системы индексирования научных работ Scopus и Web of Science. Получены 6 свидетельств о государственной регистрации программ для ЭВМ.

Свидетельства о государственной регистрации программы для ЭВМ. «Среда моделирования распознавания изображений с использованием сверточных нейронных сетей» № 2017617504 от 05.07.2017; «Программа реализации метода сглаживающей фильтрации изображений в СОК» № 2018613585 от 19.03.2018; «Среда поиска лиц на фотографии» № 2019663305 от 15.10.2019; «Среда аппаратного моделирования дискретного вейвлет-преобразования в системе остаточных классов для медицинской визуализации» № 2020612962 от 06.03.2020; «Среда аппаратного моделирования дискретного вейвлет-преобразования с квантованными коэффициентами для обработки медицинских изображений» № 2020612961 от 06.03.2020; «Среда аппаратного моделирования фильтрации изображений по методу Винограда» № 2021619007 от 03.06.2021.

Личный вклад соискателя. Все результаты диссертационного исследования получены лично автором. Из результатов работ, выполненных коллективно, в диссертацию включены только полученные непосредственно автором. В работах [3, 12, 14, 20, 21, 24, 28] автором предложены архитектуры аппаратных ускорителей слоев СНС, отвечающих за выделение признаков. В работах [1, 11] предложен метод для проектирования эффективной аппаратной реализации компонентов СНС в СОК с модулями специального вида. В статьях [2, 6, 7, 10, 13, 16-18, 27] автором представлены методы и алгоритмы увеличения производительности цифровых фильтров, а также архитектуры устройств цифровой фильтрации. В работах [4, 9, 19, 29, 31] автором разработаны подходы к реализации вычислительно сложных операций в СОК, а также спроектированы устройства на основе предлагаемых методов. В статьях [22, 23] автором предложен метод преобразования чисел из ПСС в СОК и его аппаратная реализация на основе параллельно-префиксных сумматоров. В работах [8, 25, 26, 32] автором применен метод квантования коэффициентов масок фильтров для аппаратной реализации цифровых фильтров. В работах [15, 30, 33] рассмотрено применение нейронных сетей и цифровых фильтров для решения практических задач, таких как медицинская диагностика и видеонаблюдение.

Структура диссертации. Диссертационная работа состоит из введения, 4-х глав, заключения, списка литературных источников и 2-х приложений. Содержит 48 рисунков, 19 таблиц и 1 приложение. Список используемой литературы содержит 114 источников.

# Основное содержание работы

<u>Во введении</u> обоснована актуальность темы диссертации, сформулированы цель и задачи работы, выбраны объект и предмет исследования, показаны научная новизна, практическая ценность полученных результатов, приведены основные положения, выносимые на защиту.

<u>В первой главе</u> представлена математическая модель СНС и проведен сравнительный анализ методов улучшения ее технических характеристик. Исследованы основные свойства СОК. Для улучшения характеристик аппаратной реализации СНС предложено использование СОК с модулями специального вида  $2^{\alpha}$  и  $2^{\alpha} - 1$ .

В общем виде алгоритм проектирования аппаратной реализации СНС в СОК состоит из следующих этапов:

- 1) выбор набора модулей СОК;

- 2) разработка блока преобразования из ПСС в СОК;

- 3) реализация блоков, выполняющих операцию свертки в СОК параллельно по каждому модулю системы;

- 4) квантование весовых коэффициентов, представленных действительными числами;

- 5) реализация блоков, выполняющих вычисление функций активации;

- 6) реализация блоков, выполняющих операцию выбора максимального элемента окрестности (блок max pooling);

- 7) разработка блока обратного преобразования из СОК в ПСС.

Во второй главе рассмотрена задача увеличения производительности цифровых фильтров, которые применяются для реализации операции свертки в СНС. Предложен метод проектирования цифровых фильтров на основе метода Винограда и арифметики СОК с модулями специального вида. Рассмотрены случаи наиболее распространенных на практике масок фильтров размерности  $2 \times 2$ ,  $3 \times 3$  и  $5 \times 5$ , для которых разработаны цифровые фильтры двумерной фильтрации на основе предложенного метода.

*Метод* проектирования устройства, реализующего операцию свертки на основе метода Винограда и СОК с модулями специального вида.

Двумерная фильтрация по методу Винограда в матричной форме имеет вид:

$$Z = A^{\mathrm{T}} \left( (GWG^{\mathrm{T}}) \odot (B^{\mathrm{T}}DB) \right) A, \tag{1}$$

где оператор  $\odot$  обозначает поэлементное умножение матриц, A, G и B — матрицы преобразования, W — двумерная маска фильтра, D — двумерный массив данных и Z — двумерный массив результата фильтрации. Алгоритм двумерной фильтрации по методу Винограда принято обозначать  $F(n \times n, k \times k)$ . Результат преобразования маски фильтра обозначим как  $U = GWG^T$ . Так как коэффициенты фильтра являются

константами, то данное преобразование может быть выполнено один раз предварительно. Результат преобразования входных данных D обозначим как  $V = B^T D B$ , а результат поэлементного умножения матриц как  $M = U \odot V$ . Тогда, учитывая введенные обозначения, формула (1) принимает вид  $Z = A^T M A$ .

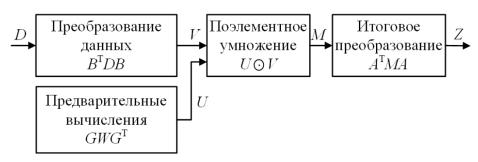

Разделим изображение на фрагменты D размера  $m \times m$ , m > k. Каждый фрагмент обрабатывается фильтром w размерности  $k \times k$  по методу Винограда  $F(n \times n, k \times k)$  с шагом n по каждому измерению. Процедура двумерной фильтрации по методу Винограда, описанная формулой (2.3.2), реализует обработку сигнала в несколько этапов (рис. 1).

Рисунок 1 – Этапы фильтрации фрагмента изображения по методу Винограда

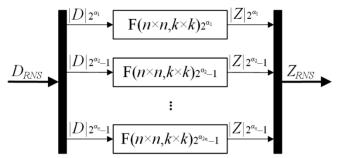

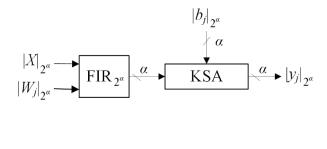

На рисунке 2 представлена архитектура предлагаемого устройства  $F(n \times n, k \times k)_{RNS}$  для фильтрации по методу Винограда в СОК с набором модулей  $\{2^{\alpha_1}, 2^{\alpha_2} - 1, \dots, 2^{\alpha_\eta} - 1\}$ . На вход устройства подается массив данных  $D_{RNS} = \{|D|_2\alpha_1, |D|_2\alpha_{2-1}, \dots, |D|_2\alpha_{\eta-1}\}$ , представленный в СОК. Затем, входные данные обрабатываются параллельно устройствами  $F(n \times n, k \times k)_2\alpha_1$ ,  $F(n \times n, k \times k)_2\alpha_{2-1}$ , ...,  $F(n \times n, k \times k)_2\alpha_{\eta-1}$ , которые формируют на выходе устройства  $F(n \times n, k \times k)_{RNS}$  массив обработанных данных  $Z_{RNS} = \{|Z|_2\alpha_1, |Z|_2\alpha_{2-1}, \dots, |Z|_2\alpha_{\eta-1}\}$ .

<u>В третей главе</u> предложены методы проектирования устройств для реализации вычислительно сложных операций в СОК, используемых в СНС.

Использование модулей вида  $\{2^{\alpha_1}, 2^{\alpha_2} - 1, \dots, 2^{\alpha_n} - 1\}$  позволяет ее избежать ресурсозатратной операции вычисления остатков от деления по каждому модулю.

*Метод* преобразования чисел из ПСС в СОК с модулями специального вида.

1. Операция вычисления остатка от деления по модулю вида  $2^{\alpha}$  осуществля-

Рисунок 2 — Архитектура устройства  $F(n \times n, k \times k)_{\text{RNS}} \text{ для двумерной фильтрации по методу Винограда в СОК с модулями вида <math>2^{\alpha}$  и  $2^{\alpha}-1$

ется простым взятием  $\alpha$  младших бит исходного числа. Введем для устройства, выполняющего вычисление остатка от деления по модулю  $2^{\alpha}$  обозначение  $MOD_{2^{\alpha}}$ .

- 2. Вычисление остатка от деления по модулю  $2^{\alpha} 1$ .

- 2.1. Пусть  $A = \sum_{i=0}^{g-1} A_i 2^i$  исходное g -битное число, представленное в ПСС битами  $A_i,\, 0 \leq i < g$  .

- 2.2. Разобьем его на  $s = \left[\frac{g}{\alpha}\right]$  частей по  $\alpha$  бит. Для этого, при необходимости, дополним A старшими значащими битами, равными 0, до размера  $g' = s\alpha$  бит.

- 2.3. Таким образом, число A' в двоичной ПСС представляется как  $A' = \sum_{i=0}^{g'-1} A_i 2^i$ , а его  $\alpha$ -битные части имеют вид  $Y_i = \sum_{j=i\alpha}^{\alpha(i+1)-1} A_j 2^j$ , где  $0 \le i < s$ .

- 2.4. Тогда число A' может быть записано как  $A' = \sum_{i=0}^{s-1} Y_i 2^{i\alpha}$ .

- 2.5. Так как  $\left| Y_i \cdot 2^{i\alpha} \right|_{2^{\alpha}-1} = |Y_i|_{2^{\alpha}-1}$ , то

$$|A'|_{2^{\alpha}-1} = \left| \sum_{i=0}^{s-1} Y_i \right|_{2^{\alpha}-1}.$$

(2)

2.6. Формула (2) показывает, что вычисление остатка от деления по модулю  $2^{\alpha}-1$  сводится к сложению  $\alpha$ -битных чисел по модулю  $2^{\alpha}-1$ . Для сложения по модулю  $2^{\alpha}-1$  больше двух слагаемых используют устройство  $\text{МОМA}_{2^{\alpha}-1}$ . Для устройства вычисления остатка от деления по модулю  $2^{\alpha}-1$  введем обозначение  $\text{MOD}_{2^{\alpha}-1}$ .

Любое целое число  $0 \le A < P$  может быть однозначно представлено в СОК как  $A = \{a_1, a_2, ..., a_n\}$ . Для представления отрицательных чисел в СОК, динамический диапазон системы делится на две примерно равные части, при этом должно выполняться одно из следующих условий

$$-\frac{P-1}{2} \le A \le \frac{P-1}{2}$$

для нечетных  $P$ ,

$$-\frac{P}{2} \le A \le \frac{P}{2} - 1$$

для четных  $P$ . (3)

Операция определения знака числа является ресурсозатратной в СОК, так как требует вычисления позиционной характеристики числа. Для вычисление позиционной характеристики числа необходимо вычислить остаток от деления на число P разрядностью равной разрядности полного диапазона системы DR. На практике, одним из самых эффективных подходов является модификация Китайской теоремы об остатках (КТО), называемая КТОд, согласно которой позиционную характеристику числа A' можно вычислить по формуле:

$$A' = \left| \sum_{i=1}^{n} a_i \tilde{k}_i \right|_{2^N},\tag{4}$$

где  $\tilde{k}_i = \left[ 2^N \frac{|P_i^{-1}|_{p_i} P_i}{P} \right]$ . Для гарантированного точного перевода чисел из СОК в ПСС

достаточно выбрать N равным:

$$N = \lceil \log_2(P\mu) \rceil,\tag{5}$$

где  $\mu = -n + \sum_{i=1}^{n} p_i$ .

Для определения знака числа в СОК по его позиционной характеристике A' необходимо выполнить проверку следующих условий:

- 1) если  $0 \le A' < 2^{N-1}$ , тогда число A положительное;

- 2) если  $2^{N-1} \le A' < 2^N$ , тогда число A отрицательное.

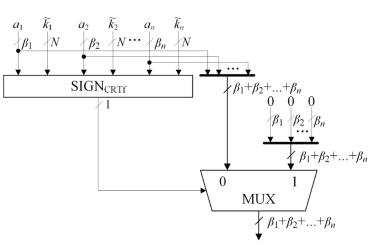

Вычисления позиционной характеристики числа с помощью КТОд производится с помощью устройства устройства NPC<sub>CRTf</sub>. На вход устройства поступает число  $\{a_1, a_2, ..., a_n\}$ , представленное в СОК с модулями  $\{p_1, p_2, ..., p_n\}$  и разрядностями  $\{\beta_1, \beta_2, ..., \beta_n\}$  по каждому модулю соответственно. Также на вход подаются коэффициенты  $\tilde{k}_i$ , имеющие разрядность N бит, они являются константами и могут быть вычислены предварительно. Генерация частичных произведений осуществляется с помощью устройств  $PPG_2\alpha$ . Далее N-битные частичные произведения складываются с помощью устройства  $MOMA_2\alpha$ . Если старший значащий бит (Most Significant Bit, MSB) числа A' равен 1, то число A отрицательное, если равен 0, то положительное. Обозначим устройство определения знака числа на основе метода КТОд как SIGN<sub>CRTf</sub>.

Функция активации ReLU требует выполнения операции определения знака числа. Архитектура устройства ReLU, представлена на рисунке 3.

*Метод* проектирования устройства, реализующего функцию активации ReLU на основе КТОд.

- 1. Определение знака числа производится с помощью устройства  $SIGN_{CRTf}$ , на вход которого поступает число  $\{a_1,a_2,\ldots,a_n\}$  и коэффициенты  $\tilde{k}_i$ .

- 2. Знак числа является управляющим сигналом мультиплексора, в соответствии с которым выбирается число  $\{a_1, a_2, \ldots, a_n\}$  или 0.

Рисунок 3 — Архитектура устройства ReLU вычисления функции активации ReLU

Операция сравнения двух чисел в СОК сводится к сравнению их позиционных характеристик. Компаратор для сравнения чисел в СОК с использованием КТОд  ${\rm COMP}_{\rm CRTf}$  состоит из двух устройств  ${\rm NPC}_{\rm CRTf}$  и устройства COMP, выполняющего сравнение двух чисел в ПСС.

*Метод* проектирования устройства, реализующего операцию выбора максимального элемента из окрестности на основе КТОд

- 1. Устройство МАХ выполняет выбор наибольшего из двух чисел, представленных в СОК в виде  $\{a_1, a_2, ..., a_n\}$  и  $\{b_1, b_2, ..., b_n\}$ , на основе КТОд.

- 1.1. На вход устройства поступают числа в СОК и их позиционные характеристики A' и B'.

- 1.2. Компаратор сравнивает A' и B' и передает управляющий сигнал на мультиплексор, в соответствии с которым выбирается число, которое больше.

- 2. Для вычисления максимального элемента из набора чисел необходимо составить дерево из нескольких устройств МАХ выбора большего из двух чисел в СОК.

Для перевода числа из СОК в ПСС предлагается устройство  $RC_{CRTf}$ , в котором с помощью устройства  $NPC_{CRTf}$  вычисляется позиционная характеристика числа A'. С помощью устройств  $PPG_{2^{\alpha}}$  и  $MOMA_{2^{\alpha}}$  (где  $\alpha$  равно N и N+DR соответственно) производится умножение A' на динамический диапазон P. Результатом являются старшие биты начиная с бита под номером N. Таким образом

$$A = \left\lfloor \frac{A'P}{2^N} \right\rfloor. \tag{6}$$

<u>В четвертой главе</u> представлен алгоритм проектирования СНС в СОК и архитектура СНС и комплекс программ на языке описания аппаратуры для аппаратной реализации СНС с использованием модулярных вычислений на FPGA.

Алгоритм проектирования аппаратной реализации СНС.

Входные данные: архитектура СНС.

Этап 1. Выбор набора модулей СОК.

В работе предлагается использовать модули СОК специального вида  $2^{\alpha}$  и  $2^{\alpha}-1$ , которые позволяют избежать затратной по ресурсам операции деления по модулю.

Этап 2. Разработка блока преобразования из ПСС в СОК.

Устройство PNS—RNS для перевода DR-битного числа A в COK с модулями вида  $\{2^{\alpha_1}, 2^{\alpha_2} - 1, \dots, 2^{\alpha_n} - 1\}$  состоит из устройств  $\text{MOD}_{2^{\alpha}}$  и  $\text{MOD}_{2^{\alpha}-1}$ . На выходе устройства PNS—RNS формируется число  $\{a_1, a_2, \dots, a_n\}$ , представленное в СОК и имеющее разрядности  $\{\alpha_1, \alpha_2, \dots, \alpha_n\}$  соответственно.

Этап 3. Реализация блоков, выполняющих операцию свертки в СОК параллельно по каждому модулю системы.

Процедура получения одной карты признаков в сверточном слое по модулю  $m_l$  может быть представлена в виде

$$\left|I_{f}(x,y)\right|_{m_{l}} = \left||b|_{m_{l}} + \left|\sum_{i=-t}^{t} \sum_{j=-t}^{t} \sum_{z=0}^{D-1} \left|W_{i,j,z}\right|_{m_{l}} \cdot \left|I(x+i,y+j,z)\right|_{m_{l}}\right|_{m_{l}}, \tag{7}$$

где  $I_f$  — карта признаков после свертки,  $W_{i,j,z}$  — это коэффициенты 3D-фильтра размерности  $d \times d$  для обработки D двухмерных массивов,  $t = \lfloor d/2 \rfloor$  и b — смещение.

Пусть  $F = \{F_0, F_1, ..., F_{D-1}\}$  – набор из D векторов размерности  $d^2$ , которые соответствуют фрагментам размерности  $d \times d$  карт признаков I, поступающих на вход сверточного слоя. Аналогично, представим маску фильтра как набор из D векторов размерности  $d^2$  и обозначим как  $W = \{W_0, W_1, ..., W_{D-1}\}$ . Операция свертки по модулю  $m_l$  для вычисления одного значения R карты признаков  $I_f$  представляется в виде:

$$|R|_{m_l} = \left| |b|_{m_l} + \left| \sum_{i=0}^{D-1} \sum_{j=0}^{d^2 - 1} |W_{i,j}|_{m_l} \cdot |F_{i,j}|_{m_l} \right|_{m_l} \right|_{m_l}.$$

(8)

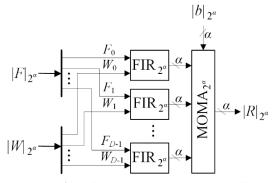

Архитектура устройства  $CONV_{2^{\alpha}}$  для свертки фрагмента изображения по модулю  $2^{\alpha}$  представлена на рисунке 4. Одномерная свертка реализуется с помощью фильтра с конечной импульсной характеристикой FIR. Результаты суммируются с помощью сумматора МОМА. Устройство свертки  $CONV_{2^{\alpha}-1}$  по модулю  $2^{\alpha}-1$  имеет аналогичную структуру, но использует технику EAC. Для реализации FIR фильтров используется метод проектирования устройства, реализующего операцию свертки на основе метода Винограда и СОК с модулями специального вида, для реализации цифровых фильтров.

Операция свертки так же применяется в полносвязных слоях нейронов, которые обычно являются заключительными слоями сети. На вход данного слоя поступает вектор входных данных  $X = \{x_i\}$ , где  $0 \le i < m, m$  – количество элементов вектора. Для каждого нейрона производится свертка входного вектора X с соответствующим вектором весовых коэффициентов  $W_j = \{w_{ji}\}$  и результат суммируется со смещением  $b_j$ , где,  $0 \le j < n, n$  – количество нейронов. Далее применяется функция активации.

На рисунке 5 представлена архитектура устройства  $FC_{2}^{\alpha}$ , выполняющего вычисления для j-го нейрона по модулю  $2^{\alpha}$ . Устройство  $FC_{2}^{\alpha}$ , выполняющее вычисления для j-го нейрона по модулю  $2^{\alpha}-1$  имеет аналогичную архитектуру, но использует технику EAC. Результаты работы устройств  $FC_{2}^{\alpha}$  и  $FC_{2}^{\alpha}$  подаются на вход устройства ReLU.

Рисунок 4 — Архитектура устройства  ${\sf CONV}_{2^\alpha} \ {\sf для} \ {\sf свертки} \ {\sf по} \ {\sf модулю} \ 2^\alpha \ {\sf фраг-}$  мента карты признаков

Рисунок 5 — Архитектура устройства  $FC_{2^{\alpha}}$  полносвязного слоя с вычислениями по модулю  $2^{\alpha}$

Этап 4. Квантование весовых коэффициентов, представленных действительными числами.

Весовые коэффициенты СНС являются вещественными числами. Для аппаратной реализации СНС требуется представить их в целочисленном виде. Для этого весовые коэффициенты необходимо умножить на  $2^p$  и округлить результат к большему целому. После выполнения вычислений, полученный результат масштабируется на  $2^{-p}$  и округляется к меньшему целому.

Этап 5. Реализация блоков, выполняющих вычисление функций активации.

На выходе сверточного слоя применяется функция активации ReLU, которая сводится к определению знака числа. Для реализации функции активации ReLU в СОК предлагается использовать устройство, представленное на рисунке 4.

Этап 6. Реализация блоков, выполняющих операцию выбора максимального элемента окрестности (блок max pooling).

Слой max pooling так же требует выполнения вычислительно сложной операции сравнения чисел в СОК. Наиболее часто на слое max pooling рассматривается окрестность размерности  $2 \times 2$ , и вычисления производятся с шагом 2. Использовался метод проектирование устройства max pooling, реализующего операцию выбора максимального элемента из окрестности на основе КТОд, описанный ранее.

Этап 7. Разработка блока обратного преобразования из СОК в ПСС.

Последним блоком системы, выполняющей вычисления в СОК, является преобразование результата обратно в ПСС. Для перевода числа из СОК в ПСС предлагается использовать метод на основе КТОд. Таким образом, архитектура устройства RNS $\rightarrow$ PNS для обратного преобразования чисел из СОК в ПСС такая же, как и архитектура устройства RC<sub>CRTf</sub>.

Выходные данные: архитектура аппаратной реализации СНС.

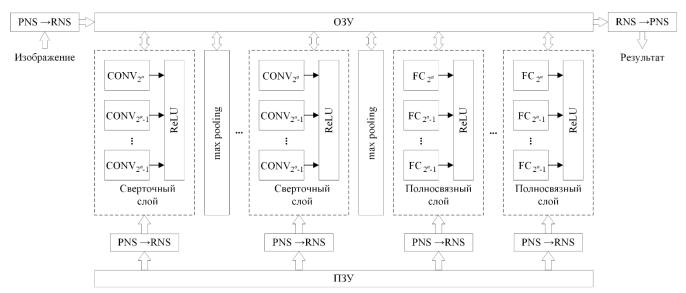

Основываясь на алгоритме проектирования аппаратной реализации СНС, разработана архитектура СНС с вычислениями в СОК с модулями специального вида

$\{2^{\alpha_1}, 2^{\alpha_2} - 1, \dots, 2^{\alpha_n} - 1\}$ , в общем виде изображенная на рисунке 6. На вход поступает изображение в виде последовательности пикселей. Сначала в блоке PNS $\rightarrow$ RNS производится преобразование данных в СОК. Затем они поступают в оперативное запоминающее устройство (ОЗУ) и передаются в другие блоки СНС (сверточные слои, слои max pooling и полносвязные слои). Весовые коэффициенты СНС хранятся в постоянном запоминающем устройстве (ПЗУ). Перевод весовых коэффициентов в СОК производится с помощью блоков PNS $\rightarrow$ RNS, затем данные в формате СОК поступают на сверточные и полносвязные слои. Результат работы СНС переводится в ПСС с помощью блока RNS $\rightarrow$ PNS и поступает на выход устройства.

Рисунок 6 – Предлагаемая архитектура СНС с вычислениями в СОК

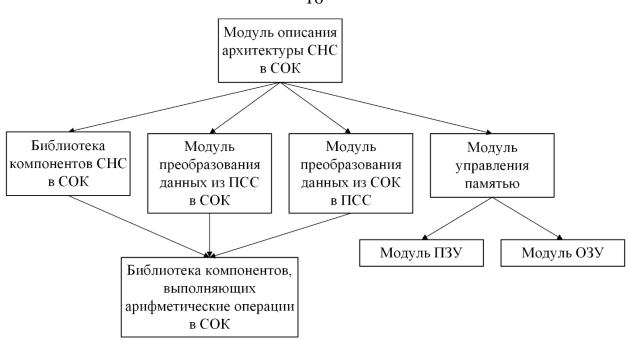

Комплекс программ на языке описания аппаратуры для аппаратной реализации сверточной нейронной сети с использованием модулярных вычислений на FPGA.

Разработанный комплекс программ состоит из следующих модулей:

- 1) модуль описания архитектуры СНС в СОК;

- 2) библиотека компонентов СНС в СОК;

- 3) библиотека компонентов, выполняющих арифметические операции в СОК.

- 4) модуль преобразования данных из ПСС в СОК;

- 5) модуль преобразования данных из СОК в ПСС;

- 6) модуль ОЗУ;

- 7) модуль ПЗУ;

- 8) модуль управления памятью.

На рисунке 7 представлена иерархическая структура взаимодействия модулей и библиотек предлагаемого комплекса программ для аппаратной реализации СНС с использованием модулярных вычислений на FPGA.

Рисунок 7 — Структура комплекса программ для аппаратной реализации СНС

Рассмотрим применение предлагаемого алгоритма для аппаратной реализации СНС с использованием СОК с набором модулей вида  $\{2^{\alpha_1}, 2^{\alpha_2} - 1, \dots, 2^{\alpha_n} - 1\}$  на примере архитектуры LeNet-5. Обучение производилось с помощью библиотек машинного обучения TensorFlow и Keras, использовался язык программирования Руthon. Функция активации гиперболический тангенс (tanh) заменена на ReLU.

Для обучения СНС использовались базы изображений MNIST, FMNIST и CIFAR-10. База MNIST содержит изображения рукописных цифр от 0 до 9 размера 28×28 в оттенках серого и состоит из 60000 изображений для обучения и 10000 изображений для тестирования. База FMNIST содержит 10 классов изображений одежды и обуви размера 28×28 в оттенках серого, состоит из 60000 изображений для обучения и 10000 изображений для тестирования. База CIFAR-10 содержит 10 классов изображений размера 32×32 формата RGB, состоит из 50000 изображений для обучения и 10000 изображений для тестирования.

Был проведен анализ влияния разрядности весовых коэффициентов СНС на точность распознавания. Было установлено, что разрядность весовых коэффициентов может быть уменьшена без потери точности распознавания. Для архитектуры СНС LeNet-5, обученной на базах MNIST и FMNIST, достаточно разрядности весовых коэффициентов 8 бит, а архитектуре, обученной на базе CIFAR-10, необходимо 12 бит.

Было проведено сравнение нескольких конфигураций архитектур СНС в зависимости от реализации сверточных слоев сети: 1) с использованием предлагаемого модифицированного метода Винограда с вычислениями в СОК с модулями специаль-

ного вида; 2) с использованием метода Винограда с вычислениями в ПСС; 3) с использованием МАС блоков в ПСС; 4) и с использованием МАС блоков с вычислениями в СОК с модулями специального вида. Устройство с вычислениями в ПСС является 32-разрядным. Для организации вычислений в СОК был выбран набор модулей  $\{2^{12}, 2^{11} - 1, 2^{10} - 1\}$ . Аппаратное моделирование было проведено в среде Xilinx Vivado 2018.3 на целевой плате Virtex-7 xc7v2000tfhg1761-2L со стратегией оптимизации AreaOpimized\_high. Результаты аппаратного моделирования представлены в таблице 2.

Для оценки эффективности были рассмотрены временные и аппаратные затраты устройств. К временным затратам относится тактовая частота устройства, измеряющаяся в МГц, и производительность, измеряющаяся количеством обработанных кадров в секунду (кадр/с). Под аппаратными затратами подразумевается занятых просмотровых таблиц (Look-Up-Table, LUT), памяти с произвольным доступом (Random Access Memory, RAM) LUTRAM и Block RAM (BRAM), а также энергопотребление устройства, которое измеряется в Вт.

Таблица 2 – Результаты аппаратного моделирования CHC LeNet-5

| Попомотр                      | Набор данных | Архитектура |        |        |        |

|-------------------------------|--------------|-------------|--------|--------|--------|

| Параметр                      |              | 1           | 2      | 3      | 4      |

| Тактовая частота, МГц         | MNIST        | 72          | 70     | 50     | 56     |

|                               | FMNIST       | 12          |        |        |        |

|                               | CIFAR-10     | 64          | 61     | 53     | 59     |

| Количество LUT                | MNIST        | 976576      | 917247 | 593291 | 647821 |

|                               | FMNIST       | 970370      |        |        |        |

|                               | CIFAR-10     | 793891      | 911182 | 612196 | 557297 |

| Количество LUTRAM             | MNIST        | 519         | 6308   | 483    | 2212   |

|                               | FMNIST       | 319         |        |        |        |

|                               | CIFAR-10     | 518         | 6369   | 483    | 2212   |

| Количество BRAM               | MNIST        | 57          | 19     | 63,0   | 181,0  |

|                               | FMNIST       | 37          |        |        |        |

|                               | CIFAR-10     | 76,50       | 25,50  | 69,5   | 200,5  |

| Энергопотребление, Вт         | MNIST        | 20,300      | 18,865 | 9,326  | 12,833 |

|                               | FMNIST       | 20,300      |        |        |        |

|                               | CIFAR-10     | 18,678      | 20,685 | 11,718 | 13,518 |

| Производительность,<br>кадр/с | MNIST        | 1556        | 1513   | 272    | 305    |

|                               | FMNIST       | 1330        |        |        |        |

|                               | CIFAR-10     | 1059        | 1009   | 221    | 246    |

Результаты моделирования показали, что использование метода Винограда позволяет увеличить производительность устройства в 4,3-5,56 раза, а применение предлагаемого подхода организации вычислений в СОК увеличивает производительность

устройства на 2,84-12,13%. Следует отметить, что использование метода Винограда привело к увеличению аппаратных затрат, таких как площадь устройства и энергопотребление.

# Основные результаты и выводы по работе

- 1. Разработан метод преобразования чисел из ПСС в СОК с модулями специального вида  $2^{\alpha}$  и  $2^{\alpha}-1$ . Выполнена программная реализация на языке описания аппаратуры VHDL предлагаемого метода. Результаты теоретического анализа и аппаратного моделирования показали, что архитектура устройства вычисления остатка от деления по модулю  $2^{\alpha}-1$  на основе предложенного метода обладает меньшей задержкой и площадью по сравнению с рассмотренными аналогами.

- 2. Разработан метод проектирования сверточных слоев СНС на основе метода Винограда и СОК с модулями специального вида. Разработаны архитектуры двумерных цифровых фильтров с масками размера 2 × 2, 3 × 3 и 5 × 5, а также программная реализация на языке VHDL для проектирования предлагаемых устройств. Результаты теоретической оценки параметров и моделирования показали, что предложенные архитектуры цифровых фильтров обладают большей производительностью по сравнению с рассмотренными аналогами, но за счет увеличения аппаратных затрат.

- 3. Разработан метод проектирования функции активации ReLU, вычисление которой сводится к операции определения знака числа, являющейся вычислительно сложной в СОК. Предложена архитектура устройства определения знака числа в СОК на основе КТОд. Разработана программная реализация на языке VHDL предлагаемого метода проектирования устройства. Результаты теоретической оценки технических параметров устройства и результаты аппаратного моделирования на FPGA показали, что разработанное устройство определения знака числа имеет меньшую задержку и площадь устройства по сравнению с рассмотренными аналогами.

- 4. Разработан метод проектирования слоя выборки максимального элемента из окрестности, требующего выполнения вычислительно сложной операции сравнения чисел в СОК. Разработана архитектура устройства сравнения чисел в СОК, использующая позиционную характеристику числа, вычисляемую на основе КТОд, а также программа на языке VHDL для проектирования предлагаемого устройства. Результаты теоретической оценки технических параметров устройства и аппаратного моделирования на FPGA показали, что предлагаемое устройство обладает меньшей задержкой и площадью по сравнению с рассмотренными аналогами. Для сравнения более чем двух чисел в слое тах pooling предлагается использовать дерево предлагаемых устройств.

- 7. Разработан алгоритм для аппаратной реализации СНС, который учитывает выбор модулей СОК, способ представления весовых коэффициентов в памяти устройства и использует разработанные оригинальные методы для проектирования компонентов СНС.

- 8. Разработан комплекс программ на языке описания аппаратуры VHDL для аппаратной реализации CHC с использованием модулярных вычислений на FPGA, включающей все разработанные методы для проектирования CHC в COK. Проведено сравнение архитектуры CHC, использующей свертку по методу Винограда в сверточном слое, и архитектуры, использующей МАС блоки. Результаты моделирования показали, что использование метода Винограда позволяет увеличить производительность устройства в 4,3-5,56 раза, а применение предлагаемого подхода организации вычислений в COK увеличивает производительность устройства на 2,84-12,13%.

# Публикации по теме диссертации

# Статьи автора в журналах, рекомендованных ВАК РФ, Scopus, Web of Science

- 1. Валуева, М.В. Метод аппаратной реализации сверточной нейронной сети на основе системы остаточных классов / М.В. Валуева, Г.В. Валуев, М.Г. Бабенко, А.Н. Черных, Х. Кортес-Мендоса // Труды Института системного программирования РАН. 2022. –№3 (34). С. 61-74.

- 2. Валуева, М.В. Высокопроизводительные архитектуры цифровой фильтрации изображений в системе остаточных классов на основе метода Винограда / М.В. Валуева, П.А. Ляхов, Н.Н. Нагорнов, Г.В. Валуев // Компьютерная оптика. 2022. Т. 46, № 5. С. 752-762.

- 3. Червяков, Н.И. Аппаратная реализация свёрточной нейронной сети с использованием вычислений в системе остаточных классов / Н.И. Червяков, П.А. Ляхов, Н.Н. Нагорнов, М.В. Валуева, Г.В. Валуев // Компьютерная оптика. 2019. Т. 43, № 5. С. 857-868.

- 4. Boyvalenkov, P. Classification of Moduli Sets for Residue Number System With Special Diagonal Functions / P. Boyvalenkov, N. Chervyakov, M. Valueva [et al.] // IEEE Access. 2020. vol. 8. P. 156104-156116.

- 5. Chervyakov, N.I. Residue Number System-Based Solution for Reducing the Hardware Cost of a Convolutional Neural Network / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva [et al.] // Neurocomputing. 2020. Vol. 407, P. 439-453.

- 6. Lyakhov, P. A Method of Increasing Digital Filter Performance Based on Truncated Multiply-Accumulate Units / P. Lyakhov, M. Valueva, G. Valuev [et al.] // Appl. Sci. 2020. Vol. 10. 9052.

- 7. Lyakhov, P. High-Performance Digital Filtering on Truncated Multiply-Accumulate Units in the Residue Number System / P. Lyakhov, M. Valueva, G. Valuev [et al.] // IEEE Access. 2020. vol. 8. P. 209181-209190.

- 8. Nagornov N.N. RNS-Based FPGA Accelerators for High-Quality 3D Medical Image Wavelet Processing Using Scaled Filter Coefficients / N.N. Nagornov, P.A. Lyakhov, M.V. Valueva [et al.] // IEEE Access. 2022 Vol. 10 P. 19215-19231.

- 9. Valueva, M. Construction of Residue Number System Using Hardware Efficient Diagonal Function / M. Valueva, G. Valuev, N. Semyonova [et al.] // Electronics. 2019. Vol. 8. № 6. 694.

- 10. Valueva, M. Digital Filter Architecture With Calculations in the Residue Number System by Winograd Method F (2×2, 2×2) / M. Valueva, P. Lyakhov, G. Valuev [et al.] // IEEE Access. 2021. vol. 9. P. 143331-143340.

- 11. Valueva, M. Method for Convolutional Neural Network Hardware Implementation Based on a Residue Number System / M. Valueva, G. Valuev, M. Babenko [et al.] // Programming and Computer Software. 2022. Vol. 48, No. 8. P. 735–744.

- 12. Valueva, M.V. Application of the residue number system to reduce hardware costs of the convolutional neural network implementation / M.V. Valueva, N.N. Nagornov, P.A. Lyakhov [et al.] // Mathematics and Computers in Simulation. 2020. Vol. 177. P. 232-243.

# Другие публикации автора по теме диссертации

- 13.Валуева М.В. Архитектуры устройств двумерной фильтрация по методу винограда F(2x2,2x2) с вычислениями в системе остаточных классов // Современная наука и инновации. -2021. -№ 3 (35). C. 41-52.

- 14.Валуева М.В. Разработка аппаратной реализации нейросетевого классификатора визуальных образов с использованием вычислений в системе остаточных классов // Сборник тезисов участников форума "Наука будущего наука молодых". Нижний Новгород. 2017. С. 107-108.

- 15. Ляхов, П.А. Аппаратная реализация устройства обработки видео с использованием системы остаточных классов / П.А. Ляхов, А.С. Ионисян, В.В. Масаева, М.В. Валуева // Современная наука и инновации. − 2021. − №1 (33). − С. 15-21.

- 16. Ляхов, П.А. Высокопроизводительная цифровая фильтрация на модифицированных умножителях с накоплением в системе остаточных классов с модулями специального вида / П.А. Ляхов, А.С. Ионисян, М.В. Валуева, А.С. Ларикова // Информационные технологии. 2021. Т. 27. №4. С. 171—179.

- 17. Ляхов, П.А. Модифицированные умножители с накоплением для повышения производительности цифровых фильтров / П.А. Ляхов, А.С. Ионисян, М.В. Валуева,

- А.С. Ларикова // Инфокоммуникационные технологии. -2020. Т. 18. № 4. С. 403-410.

- 18. Ляхов, П.А. Применение сглаживающих фильтров для очистки от шума изображений в оттенках серого / П.А. Ляхов, М.В. Валуева // Наука. Инновации. Технологии. -2015. -№3. С. 37-50.

- 19. Семенова, Н.Ф. Построение системы остаточных классов с диагональной функцией специального вида / Н.Ф. Семенова, Н.И. Червяков, П.А. Ляхов, М.В. Валуева, Г.В. Валуев // Современная наука и инновации. 2019. №4 (28). С. 10-21.

- 20. Червяков, Н.И. Архитектура сверточной нейронной сети с вычислениями в системе остаточных классов с модулями специального вида / Н.И. Червяков, П.А. Ляхов, Д.И. Калита, М.В. Валуева // Нейрокомпьютеры: разработка, применение. 2017. №1. С. 3-15.

- 21. Червяков, Н.И. Архитектура сверточной нейронной сети с извлечением признаков в системе остаточных классов / Н.И. Червяков, П.А. Ляхов, М.В. Валуева, Н.Н. Нагорнов, Г.В. Валуев // Мягкие измерения и вычисления. 2019. №5. С. 25-36.

- 22. Червяков, Н.И. Применение сумматоров с параллельно-префиксной архитектурой для перевода чисел из двоичной системы счисления в систему остаточных классов / Н.И. Червяков, П.А. Ляхов, Н.Ф. Семенова, М.В. Валуева // Нейрокомпьютеры: разработка, применение. 2016. №10. С. 31-39.

- 23. Червяков, Н.И. Сравнительный анализ аппаратной реализации сумматоров на FPGA / Н.И. Червяков, П.А. Ляхов, М.В. Валуева, О.В. Криволапова // Наука. Инновации. Технологии. 2016. №4. С. 99-108.

- 24. Chervyakov, N.I. Area-Efficient FPGA Implementation of Minimalistic Convolutional Neural Network Using Residue Number System / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva [et al.] // 2018 23rd Conference of Open Innovations Association (FRUCT). 2018. P. 112-118.

- 25.Chervyakov, N.I. High-Performance Hardware 3D Medical Imaging using Wavelets in the Residue Number System / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva [et al.] // 2020 9th Mediterranean Conference on Embedded Computing (MECO). 2020. P. 1-4.

- 26.Chervyakov, N.I. High-Quality 3D Medical Imaging by Wavelet Filters with Reduced Coefficients Bit-Width / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva [et al.] // 2019 International Conference on Engineering and Telecommunication (EnT). 2019. P. 1-5.

- 27. Chervyakov, N.I. High-speed smoothing filter in the Residue Number System / N. I. Chervyakov, P. A. Lyakhov, M.V. Valueva, [et. al.] // 2016 Third International Conference on Digital Information Processing, Data Mining, and Wireless Communications (DIPDMWC). 2016. P. 121-126.

- 28. Chervyakov, N.I. Increasing of Convolutional Neural Network Performance Using Residue Number System / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva. // International Multi-Conference on Engineering, Computer and Information Sciences (SIBIRCON). 2017. P. 135–140.

- 29. Chervyakov, N.I. On RNS with VLSI-friendly diagonal function / N.I. Chervyakov, P.A. Lyakhov, M.V. Valueva [et. al.] // 2017 International Multi-Conference on Engineering, Computer and Information Sciences (SIBIRCON). 2017. P. 131-134.

- 30. Kaplun, D.I. Hardware Implementation of Video Processing Device using Residue Number System / D.I. Kaplun, N.I. Chervyakov, M.V. Valueva [et al.] // 2019 42nd International Conference on Telecommunications and Signal Processing (TSP). 2019. P. 701-704.

- 31.Lyakhov, P.A. A New Method of Sign Detection in RNS Based on Modified Chinese Remainder Theorem / P.A. Lyakhov, M.V. Valueva, D.I. Kaplun [et al.] // 2021 10th Mediterranean Conference on Embedded Computing (MECO). 2021. P. 1-4.

- 32.Lyakhov, P.A. Low-Bit Hardware Implementation of DWT for 3D Medical Images Processing / P.A. Lyakhov, M.V. Valueva, N.N. Nagornov // 2020 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus). 2020. P. 1396-1399.

- 33.Lyakhov, P.A. Single Image Super-Resolution Method Based on Bilinear Interpolation and U-Net Combination / P.A. Lyakhov, G. V. Valuev, M. V. Valueva [et al.] // 2021 10th Mediterranean Conference on Embedded Computing (MECO). 2021. P. 1-4.